# **Scalable Translation Validation**

# **Tools, Techniques and Framework**

# DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

# Doktor der technischen Wissenschaften

by

Dipl.-Ing. Roland Lezuo

Registration Number 0227059

to the Faculty of Informatics at the Vienna University of Technology

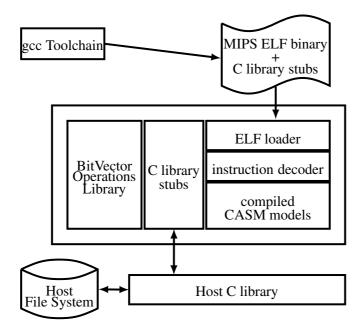

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr. Andreas Krall

The dissertation has been reviewed by:

(Ao.Univ.Prof. Dipl.-Ing. Dr. Andreas Krall) (Prof. Dr. rer. nat. habil. Wolf Zimmermann)

Wien, 20.03.2014

(Dipl.-Ing. Roland Lezuo)

# Erklärung zur Verfassung der Arbeit

Dipl.-Ing. Roland Lezuo Burggasse 35/1, 1070 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

For Maya

# Acknowledgments

First I want to thank my wife for her encouraging support and understanding during this time of ups and downs and my children for cheering me up as only children can.

Many thanks to my advisor, Andreas Krall, for letting me pursue the topic with such a high degree of freedom and personal responsibility. The trust he put into me was always motivating for me. I also want to thank Wolf Zimmermann for the enlightening discussion on the topics of programming language semantics and translation validation. Without his support this work would not have been possible. And last, but not least, I want to thank Laura Kovács for her invaluable support regarding theorem provers.

I also want to mention all my colleagues at the Complang group in Vienna which always made going to the office a joy. Especially I want to emphasize Gergö Barany for his precise comments on paper drafts and fruitful discussion on CASM and Ioan Dragan for his collaboration regarding vanHelsing. Special thanks go to Dominik Inführ and Philipp Paulweber for their commitment to provide solid implementations of my prototypes. And very special thanks to my sister Cornelia for her heroic proof reading.

**Funding:** This work is partially supported by the Austrian Research Promotion Agency (FFG) under contract 827485, Correct Compilers for Correct Application Specific Processors and Catena DSP GmbH.

# Abstract

Today embedded computer systems are often used in safety-critical applications. A malfunction in such a system (e.g. X-by-wire) often has severe effects, even life-threatening consequences. Lots of effort is put into certification to assure the correct and safe behavior of safety-critical applications. Due to the high complexity of modern technical systems, a high-level programming language like C is commonly used to implement their software.

This makes the compiler a critical component in the certification of safety-critical systems. Even if the source code is fully certified and error-free an erroneous compiler could introduce unintended behavior and hence the certification would be in vain. This is one motivation of research in compiler correctness, a discipline which develops methods to show that the compiler behaves correctly. One approach, namely translation validation, formally proves that a single, specific run of the compiler was error-free.

This thesis contributes a framework which allows to apply translation validation from the source code down to its binary representation. The CASM language, based on the formal method of Abstract State Machines (ASM), has been developed as part of this thesis to specify the semantics of the source language and machine code. Using the novel technique of direct symbolic execution a first-order logic representation is created as the foundation for the formal proofs. To exploit the common structure found in problems originating from translation validation problems a specialized prover called vanHelsing has been implemented as part of this thesis. Its visual proof debugger enables non-domain experts to analyze failing proofs and pinpoint the causing, erroneous translation.

The detailed evaluation shows that CASM is by far the best performing ASM implementation. It is efficient enough to synthesize Instruction Set Simulation and Compiled Simulation tools. The vanHelsing prover performs much better than other state of the art provers on problems stemming from translation validation. These efficient tools and the high degree of parallelism in our translation validation framework enable fast validations. The implemented prototypes for instruction selection, register allocation and VLIW scheduling demonstrate that validation of real-world applications like *bzip2* is possible within a few dozen minutes.

# Kurzfassung

Viele der heute verwendeten eingebetteten Computersysteme übernehmen sicherheitskritische (*safety-critical*) Aufgaben. Die Fehlfunktion eines sicherheitskritischen Systems führt per Definition zu großen Schäden, unter ungünstigen Umständen auch zur Gefahr für Leib und Leben. Teure Zertifizierungsverfahren werden durchlaufen um das korrekte und sichere Verhalten solcher Systeme sicherzustellen. Aufgrund der allgemein hohen Komplexität moderner technischer Systeme wird die Software, auch von sicherheitskritischen Anwendungen, oft in Hochsprachen wie C implementiert.

Dadurch wird der Übersetzer (*compiler*) dieser Sprache zertifizierungsrelevant. Selbst wenn der zugrunde liegende Quellcode der Software bewiesenermaßen fehlerfrei ist kann ein einziger Übersetzungsfehler ein verändertes Verhalten in der Ausführung bewirken. Dieser würde jedoch die komplette Zertifizierung obsolet machen, eine Motivationen für Forschung im Gebiet der Übersetzerkorrektheit (*compiler correctness*), einer Disziplin welche Techniken und Methoden erforscht um mit Hilfe formaler Verfahren die Korrektheit von Übersetzern sicherzustellen. Ein methodisches Vorgehen, die sogenannte *Translation Validation*, prüft dabei a posteriori die semantische Äquivalenz des Quellcodes mit dem übersetzten Programm.

Diese Dissertation beschreibt einen strukturellen Ansatz, welcher es ermöglicht, alle Schritte einer Übersetzung mit der *Translation Validation* Methode zu verifizieren. Um eine präzise Beschreibung der Semantik des Quellcodes und der ausführenden Maschine zu erstellen wurde, basierend auf der Theorie der *Abstract State Machine (ASM)*, eine geeignete Sprache (CASM) spezifiziert und implementiert. Durch die innovative Technik der direkten symbolischen Ausführung von ASM kann die Semantikspezifikation konkreter Programme in Prädikatenlogik erster Stufe dargestellt werden. Diese Darstellung bildet die Grundlage für den formalen Beweis der Übersetzerkorrektheit. Die sich ergebenden Beweisverpflichtungen weisen eine gemeinsame, problembezogene Struktur auf. Der im Zuge dieser Arbeit entwickelte vanHelsing Beweiser ist in Hinblick auf diese Struktur optimiert. Die Möglichkeit nicht bewiesene Probleme grafisch zu untersuchen bietet, auch ungeübten Anwendern von Theorembeweisern, ein Werkzeug um die jeweilige Ursache in der Problemdomäne zu identifizieren.

In der ausführlichen empirischen Untersuchung wird gezeigt, dass die CASM Sprache wesentlich schnellere Programmausführung ermöglicht als andere ASM Implementierungen. Die Geschwindigkeit ist hoch genug um sowohl Befehlssatz Simulatoren (*Instruction Set Simulator*) als auch übersetzende Simulation (*compiled simulation*) aus den CASM Spezifikationen der Maschine zu erzeugen. Der vanHelsing Beweiser ist, für Probleme hinsichtlich derer er optimiert wurde, wesentlich schneller als andere Theorembeweiser. Erst diese effizienten Implementierungen ermöglichen dass die Laufzeiten, der im Zuge dieser Arbeiten erstellten Prototypen für *Translation Validation* (Codeerzeugung, Registerzuteilung und Befehlsanordnung für VLIW Maschinen), selbst für realistisch große Programme wie z.B.: *bzip2*, jeweils nur wenige Minuten betragen.

# List of used Acronyms

- **ABI** Application Binary Interface

- ADL Architecture Description Language

- ALU Arithmetic Logic Unit

- **ASM** Abstract State Machine

- **AST** Abstract Syntax Tree

- **ATP** Automated Theorem Proving

- **BV** Bit Vector

- **CFA** Control Flow Association

- **CFG** Control Flow Graph

- cLIR causal LIR

- **CS** Compiled Simulation

- **DFT** Data Flow Tree

- **DSL** Domain Specific Language

- **EBNF** Extended Backus-Naur Form

- **EMF** Eclipse Modeling Framework

- **FFT** Fast Fourier Transformation

- **FU** Functional Unit (part of CPU dedicated to specific operation)

- **FUF** FU Field (part of internal state of a FU)

- **FV** Field Value (decoded field of an instruction)

- **ILP** Instruction Level Parallelism

- **IR** Intermediate Representation

- **ISS** Instruction Set Simulation

- **LASM** Linked Assembly Module

- LIR Low-level IR

- LOC Lines of Code

- MIR Mid-End IR

- **mMIR** matcher MIR

- SIMD Single Instruction Multiple Data

- sLIR scheduled LIR

- **SMT** Satisfiability Modulo Theories

- **STS** State Transition System

- **SSA** Static Single Assignment

- **VLIW** Very Long Instruction Word

- XML eXtensible Markup Language

# Contents

| 1 | Intr                                                               | oduction                                                                                                                                                                                                                                                                                                           | 1                                                          |  |  |  |

|---|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| 2 | <b>Rela</b><br>2.1<br>2.2<br>2.3                                   | Ited Work         Compiler Verification         Abstract State Machines         First-Order Theorem Provers                                                                                                                                                                                                        | <b>5</b><br>5<br>7<br>8                                    |  |  |  |

| 3 | CASM - Efficient Abstract State Machines 11                        |                                                                                                                                                                                                                                                                                                                    |                                                            |  |  |  |

|   | 3.1                                                                | CASM - An Implementation of ASM                                                                                                                                                                                                                                                                                    | 11                                                         |  |  |  |

|   | 3.2                                                                | Direct symbolic execution of ASM                                                                                                                                                                                                                                                                                   | 14                                                         |  |  |  |

|   | 3.3                                                                | Efficient Compilation of CASM                                                                                                                                                                                                                                                                                      | 20                                                         |  |  |  |

| 4 | Sem                                                                | antics and Compilers                                                                                                                                                                                                                                                                                               | 25                                                         |  |  |  |

|   | 4.1                                                                | ADL for Retargetable Compilers                                                                                                                                                                                                                                                                                     | 25                                                         |  |  |  |

|   | 4.2                                                                | Compiler Overview                                                                                                                                                                                                                                                                                                  | 27                                                         |  |  |  |

|   | 4.3                                                                | Semantics of Compiler IR                                                                                                                                                                                                                                                                                           | 28                                                         |  |  |  |

|   | 4.4                                                                | A unified Machine Model                                                                                                                                                                                                                                                                                            | 31                                                         |  |  |  |

| 5 | Proof Techniques 3:                                                |                                                                                                                                                                                                                                                                                                                    |                                                            |  |  |  |

|   | 5.1                                                                | Program Checking                                                                                                                                                                                                                                                                                                   | 35                                                         |  |  |  |

|   | 50                                                                 | Simulation Proofs                                                                                                                                                                                                                                                                                                  | 35                                                         |  |  |  |

|   | 5.2                                                                |                                                                                                                                                                                                                                                                                                                    | 55                                                         |  |  |  |

| 6 |                                                                    | Big Picture - Chain of Trust                                                                                                                                                                                                                                                                                       | 55<br>41                                                   |  |  |  |

| 6 |                                                                    |                                                                                                                                                                                                                                                                                                                    |                                                            |  |  |  |

| 6 | The                                                                | Big Picture - Chain of Trust                                                                                                                                                                                                                                                                                       | <b>41</b><br>42<br>44                                      |  |  |  |

| 6 | <b>The</b><br>6.1                                                  | Big Picture - Chain of Trust         Definition of Correct Compilation         Front-end         Mid-end - Verification of Analyses                                                                                                                                                                                | <b>41</b><br>42<br>44<br>44                                |  |  |  |

| 6 | <b>The</b> 6.1 6.2 6.3 6.4                                         | Big Picture - Chain of Trust         Definition of Correct Compilation         Front-end         Mid-end - Verification of Analyses         Back-end - Verification of Transformations                                                                                                                             | <b>41</b><br>42<br>44<br>44<br>45                          |  |  |  |

| 6 | <b>The</b> 6.1 6.2 6.3                                             | Big Picture - Chain of Trust         Definition of Correct Compilation         Front-end         Mid-end - Verification of Analyses                                                                                                                                                                                | <b>41</b><br>42<br>44<br>44                                |  |  |  |

| 6 | <b>The</b> 6.1 6.2 6.3 6.4 6.5                                     | Big Picture - Chain of Trust         Definition of Correct Compilation         Front-end         Mid-end - Verification of Analyses         Back-end - Verification of Transformations                                                                                                                             | <b>41</b><br>42<br>44<br>44<br>45                          |  |  |  |

|   | <b>The</b> 6.1 6.2 6.3 6.4 6.5                                     | Big Picture - Chain of Trust         Definition of Correct Compilation         Front-end         Mid-end - Verification of Analyses         Back-end - Verification of Transformations         Multiple Iterated Passes         Frectness of Selected Back-end Transformations         Prolog and Epilog Insertion | <b>41</b><br>42<br>44<br>44<br>45<br>45                    |  |  |  |

|   | The<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>Cor                      | Big Picture - Chain of Trust         Definition of Correct Compilation         Front-end         Mid-end - Verification of Analyses         Back-end - Verification of Transformations         Multiple Iterated Passes         Freetness of Selected Back-end Transformations                                     | <b>41</b><br>42<br>44<br>44<br>45<br>45<br>45<br><b>47</b> |  |  |  |

|   | <b>The</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br><b>Cor</b><br>7.1 | Big Picture - Chain of Trust         Definition of Correct Compilation         Front-end         Mid-end - Verification of Analyses         Back-end - Verification of Transformations         Multiple Iterated Passes         Frectness of Selected Back-end Transformations         Prolog and Epilog Insertion | <b>41</b><br>42<br>44<br>45<br>45<br>45<br><b>47</b><br>47 |  |  |  |

|     | 7.5    | Software Pipelining                                 | 56  |

|-----|--------|-----------------------------------------------------|-----|

|     | 7.6    | Register Allocation & Spilling                      | 58  |

|     | 7.7    | Stack Finalization                                  | 61  |

|     | 7.8    | Linking                                             | 61  |

|     | 7.9    | Summary                                             | 62  |

| 8   | vanH   | Ielsing: Prover and Debugger                        | 63  |

|     | 8.1    | Input Language                                      | 64  |

|     | 8.2    | Implementation                                      | 65  |

|     | 8.3    | Proof Debugger                                      | 67  |

|     | 8.4    | Defining Expressions                                | 69  |

| 9   | Instr  | ruction Set Simulation & Compiled Simulation        | 71  |

|     | 9.1    | Instruction Set Simulation                          | 71  |

|     | 9.2    | Instruction Set Simulator Verification              | 72  |

|     | 9.3    | Compiled Simulation                                 | 75  |

| 10  | Eval   | uation                                              | 79  |

|     | 10.1   | CASM implementation                                 | 79  |

|     |        | vanHelsing Prover                                   | 89  |

|     | 10.3   | Translation Validation                              | 90  |

| 11  | Futu   | ire Work                                            | 97  |

|     |        | CASM Object Model                                   | 97  |

|     |        | Update Placement Optimization for the CASM Compiler | 97  |

|     |        | Translation Validation of the CASM Compiler         | 98  |

|     | 11.4   | Synthesization of the Compiler Specification        | 98  |

| 12  | Cone   | clusion                                             | 99  |

| Bil | oliogr | aphy                                                | 101 |

| A   | Voca   | bulary and Axioms                                   | 109 |

| B   | The    | CASM Language                                       | 119 |

| С   | vanH   | Helsing Input Language                              | 125 |

| D   | Colo   | phon                                                | 129 |

| Е   | Curi   | riculum Vitae                                       | 131 |

# Introduction

The number of embedded systems used in everyday life has increased significantly in the last decade and will increase further. With the increasing prevalence, more and more systems are used in safety-critical applications. According to Wikipedia a malfunction of a safety-critical system may result in death or serious injury to people, or loss of severe damage to equipment or environmental harm. To manage the complexity, software used to operate critical systems is often written in a high-level programming language, like C. There are industry-wide standards on the usage of C in such systems, e.g. MISRA C:2004<sup>1</sup>, a *guideline to the use of the C language in critical systems*.

To assure the correctness of safety-critical systems a significant effort is put into their verification. A good point in case is the seL4 micro-kernel [40], a kernel for security-critical applications with high reliability demands. It has been shown that this approximately 10.000 Lines of Code (LOC) C program is consistent with its specification models and free of a large class of common bugs (including null pointer access, alignment constraints, termination, processing unchecked user data). The manual labor put in (and therefore the costs of) such a verification are very high, i.e. many person years of work. The result of the verification is a trusted base of C code.

But the guaranteed properties of verified source code do not imply that those properties hold in the embedded system. The source code is compiled to the target hardware and executed by a real micro-processor, and both, the compiler and the hardware, may be erroneous. Hardware verification is a well studied problem and today's designs are at least partially verified [37]. Although there exist hardware bugs (e.g. the famous Intel FDIV bug <sup>2</sup>) they are much less problematic than software bugs in today's systems.

<sup>&</sup>lt;sup>1</sup>http://www.misra.org.uk/

<sup>&</sup>lt;sup>2</sup>http://en.wikipedia.org/wiki/Pentium\_FDIV\_bug

# 1 Introduction

All it takes to invalidate the verification results is a single compilation error resulting in a behavioral difference between source code and binary. Such an change in behavior invalidates the preconditions made to verify the source code, and thous the results don't hold for the binary. A recent study by Yang et al. [68] reports on a large scale random testing of 11 C compilers including GCC, LLVM and CompCert [43]. They found silently erroneous compiled code in every single compiler, including the CompCert compiler, which is the only major commercial available (in large parts) verified C compiler. The conclusion is that compiler errors are probably more common than anticipated and can not be ignored in safety-critical systems.

Compiler verification is the field of research which deals with methods and techniques to show that a compiler behaves as specified. A verified compiler is a compiler for which has been shown that it is error-free, i.e. each program translated with a verified compiler is errorfree. A disadvantage of this approach is that the smallest change in the compiler triggers a full re-verification. The other major approach is translation validation, which does not show that the compiler is correct, but that a specific, single compilation is correct. The compiler itself may contain errors, but they do not matter as long as those errors do not manifest themselves (i.e. changing the behavior of the binary). One advantage of this approach is that the compiler can be developed using common software engineering techniques, the disadvantage is that the validation has to be performed for each compilation.

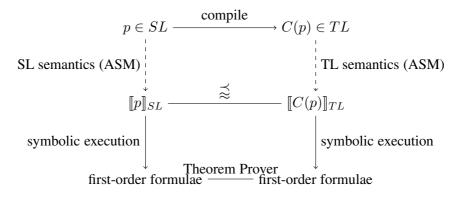

To apply translation validation the *semantics* of the source and target languages must be known *concisely (formally)*. The proof itself relies on formal methods and tools. Automated Theorem Proving (ATP) is an established field of research and a number of mature theorem provers is available. The method presented in this thesis makes use of that knowledge by creating a problem formulation suitable for ATP tools.

#### Contribution

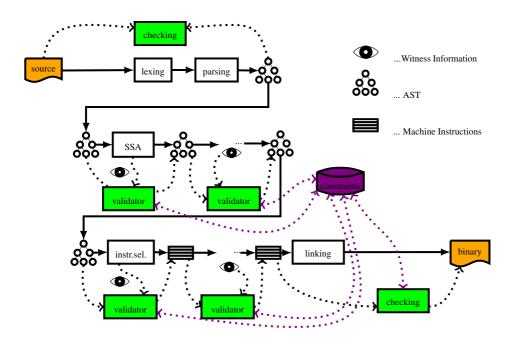

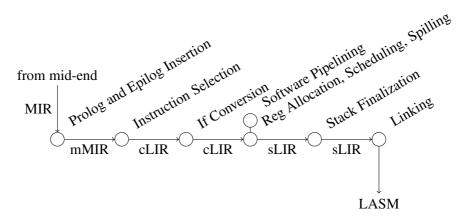

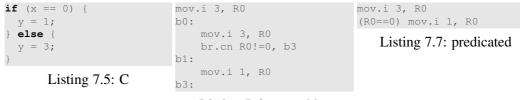

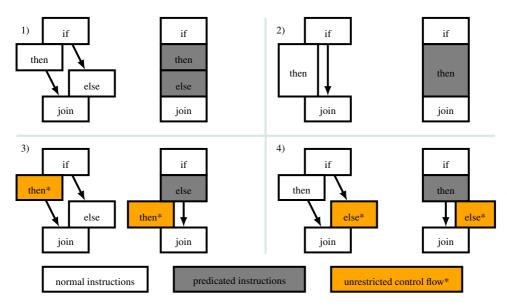

This thesis contributes to the field of compiler verification by developing scalable, fully automated methods which allow to verify the whole compilation process (from source to binary). A translation validation framework is proposed which splits the validation task along compiler passes. This allows each pass to be validated in isolation (*local correctness*), keeping the validators simple. The validators further split the validation task along basic blocks of the program. This gives a very high degree of parallelism which can be exploited to achieve fast validation even for very large programs. The framework allows to extend those *local* proofs to the notion of a *global* correctness.

We developed a variant of Abstract State Machine (ASM), called CASM, to formally specify the semantics of the involved languages. The novel technique of *direct symbolic execution* is used to create first-order logic representations of the CASM specifications, which allows the use of theorem provers.

Another contribution of this work is the vanHelsing theorem prover. This prover is specialized for the type of problems stemming from translation validation. Due to the specialization on this specific class of problems it also delivers excellent performance. A distinct feature is its support for graphical debugging failing proofs. This allows to analyze problems in proofs without expert knowledge in theorem proving. Even a novice user is able pinpoint the causing issue in the *problem domain*. We also feel that verification in an industrial context should not be an isolated task. Therefore we developed tools to reuse the semantic models to synthesize instruction set simulators and perform compiled simulation. We argue that a single rigorous (formal) specification of the hardware is sufficient for verification, and synthesization of Instruction Set Simulation (ISS) and Compiled Simulation (CS) tools.

# Layout of the Thesis

The remainder of this thesis is structured as follows: Chapter 2 discusses related work in the field of compiler verification, ASM and first-order theorem provers. Chapter 3 introduces the CASM language developed as part of this thesis. It defines the novel method of *direct symbolic execution* and describes the optimizing compiler. In chapter 4 the semantic aspects of compiler Intermediate Representations (IRs) are presented. A method to specify the semantics for a retargetable compiler for application specific processors is given. The technical aspects of creating IR dumps as CASM programs are presented. Chapter 5 introduces the proof techniques used in this work. The simulation proof technique and the common semantic vocabulary are a core concept of this thesis.

After the technical foundations have been laid chapter 6 presents our translation validation framework and describes the verification from C source code down to machine code. The definition of the term *correct compilation* is given. Front-end and mid-end are discussed, while the focus of this thesis is on the compiler back-end. In chapter 7 the validator tools for specific back-end passes developed in this work are presented. This chapter is the technical core of this thesis. Chapter 8 describes the vanHelsing prover, a fully-mechanized first-order theorem prover developed as part of this thesis. The main motivation to implement a custom prover is its ability to provide graphical debugging aids for failing proofs. vanHelsing is specialized on a specific class of proof class and argues why a specific prover performs significantly better than more general theorem provers. Chapter 9 describes the implementation details of ISS and CS based on the CASM models. Chapter 10 reports on the performance of the methods developed in this work. We present benchmark data of selected validator prototypes, the vanHelsing prover and our ISS and CS implementations. In chapter 11 possible extensions to the tools and open issues which were not addressed by this work are discussed, and chapter 12 finally concludes this thesis.

# 2

# **Related Work**

# 2.1 Compiler Verification

Compiler verification is a very old idea with its roots in the 1960s. One idea is to prove that a compiler will only generate correct code. In this work we call this a verified compiler *in the strict sense*. The main disadvantage of this approach is that any change in the compiler triggers a complete re-verification. A verified compiler is therefore a piece of software set in stone.

Nonetheless Leroy's CompCert [43], the most important commercial available verified compiler, is a verified compiler *in the strict sense*. Large parts of CompCert are specified in Coq [9], an interactive proving tool which allows to extract executable code out of a specification. The compiler front-end (parser, type-checker and simplifier) and the assembler output module are not verified, though. With Yang et al. [68] recently finding serious bugs in the simplifier a complete source-to-binary verification seems to be necessary. The CompCert approach also fully trusts the assembler (creating the binary representation of the assembler language) and linker. Our approach covers parsing and linking.

The second important approach to compiler verification is translation validation. It has been suggested by Pnueli [57] and only verifies that a specific compilation is correct. The idea is similar to program checking [10]. An external observer (the validator) determines the correctness of an computation by inspection of the input and the calculated output. After a source program has been translated by an unverified compiler a validator tries to prove the target program to be a correct compilation. The proofs are performed by simulating source and target in a common semantic framework. The motivation of translation validation is that the validator may be significantly easier to write (and verify) than the compiler itself. In addition the software development process of the compiler is unconstrained (as changes don't trigger expensive re-verification).

Zimmermann and Gaul showed that this approach can be applied to realistic compilers (Verifix project [70]). They suggested ASM to build the common semantic framework, an idea also

# 2 Related Work

used in this work. Tree pattern matching rules are partially checked when generating the Verifix back-end, it is therefore (partly) verified *in the strict sense*. It is also entangled with register allocation. Our approach separates these passes and fully validates tree pattern matching at compile time.

Zuck et al. present VOC, a translation validation framework and tool for an optimizing compiler. They focus on the compiler IR and optimizations performed on it but do not cover machine code. Otherwise their notation of correctness is very similar to ours. Using a common semantic framework to describe source and target program they rely on *simulation* proofs to show that the target is a *refinement* of the source. Our approach is more general as we allow the source and target program to be in different IR languages. The validation tool operates on functions and considers whole paths through the function which may lead to scalability issues for large functions. Our approach operates on basic blocks which are on average significant smaller. They also discuss structure changing loop transformations which are quite hard to validate. In contrast to our work they do not consider pointers and aliasing at all.

Leviatan [44] presents a translation validation tool for software pipelining. They derive a large number (depending on the number of parallel stages) of correctness conditions to be verified. Pointers and aliasing is also not handled by this approach.

In [53] Necula describes a translation validation tool for an unmodified version of the GCC compiler. His approach operates on GCC's IR directly which is dumped before and after each optimization pass has been performed. Using a small set of heuristics enables identification of the applied transformations in the majority of the cases (i.e. there are false negatives). As in our approach symbolic execution of basic blocks combined with tracking of liveness information yields a good scalability. The main limitations of this approach are that it is unclear how to extend it to machine code as it operates on GCC IR directly.

More work on compiler verification can be found in Maulik's bibliography [20].

# Differentiation

Figure 2.1 compares the discussed approaches with respect to various features. A ++ means very well suited, + means well suited, - means not so well and - - finally is not well suited. An important aspect is whether the approach can handle the whole compilation, that is from source down to binary (*source-to-binary*). Providing witness information means that the compiler must be changed which is an undesirable property for industrial application. By *scalability* we mean whether the method can cope with large programs. Modern industrial compilers transform programs in multiple (probably repeated) passes. Splitting the validation into passes is therefore important (*multi-pass compilers*). The effort to create a validator for an additional pass is an important aspect for industrial acceptance of translation validation. And finally the size of the trusted code base matters. The larger it is the more effort (and monetary resources) must be put into its certification.

|                            | CompCert | Necula | VOC | Verifix | this work |

|----------------------------|----------|--------|-----|---------|-----------|

| source-to-binary           | -        |        |     | ++      | ++        |

| compiler-provided witness  | ++       | +      | -   | -       | -         |

| scalability                | ++       | ++     | -   | -       | ++        |

| multi-pass compilers       | +        | ++     | +   | -       | ++        |

| effort for additional pass |          | +      | +   | -       | ++        |

| size of trusted code-base  | -        | ++     | ++  | +       | +         |

Figure 2.1: Compiler verification feature matrix

# 2.2 Abstract State Machines

ASM was introduced by Gurevich (originally named evolving algebras) in the Lipari Guide [31]. The original motivation was to bridge the gap created by the computational model of Turing machines. A coding-free technique to describe algorithms on a *natural abstraction level* was sought.

The ideas of ASMs were further developed by Gurevich and others at Microsoft Research resulting in a powerful specification language called AsmL [33]. AsmL is designed to be simple, precise, executable, testable, inter operable, integrated, scalable and analyzable. The language is statically typed, supports object oriented features, has call-by-value semantics and supports exceptions. An efficient compiler for .NET has been developed and the language has been fully integrated into the .NET framework and the Microsoft development environment [7]. The tool environment comprehends *parameter generation* for providing method calls with parameter sets, *finite state machine* generation from an ASM, *sequence generation* for deriving test sequences and *run-time verification* for testing if an implementation performs conforming to the model. The tool environment around AsmL is the most advanced currently available.

One of the most performance critical issue in ASMs is the problem of partial updates. Gurevich and Tillmann discussed the problem in detail and showed how concurrent data modifications can be implemented efficiently [34]. Similar problems occur in version control systems on software merging [52]. Techniques which work only on the delta (the differences) of the data sets inspire optimizations on efficient update implementation in CASM.

Castillo describes the ASM Workbench in [17]. Similar to CASM he added a type system to his language. The ASM Workbench is implemented in  $ML^1$  in an extensible way. Castillo describes an interpreter and a plugin for a model checker, which allows to translate certain restricted classes of ASMs to models for the SMV<sup>2</sup> model checker.

Schmid describes compiling ASM to C++ [60]. The compiler uses the ASM Workbench language as input. He proposes a double buffering technique avoiding implementing update sets at all. This approach is limited to parallel execution semantics only, though.

Schmid also introduced AsmGofer in [61]. AsmGofer is an interpreter for an ASM based language. It is written in the Gofer<sup>3</sup> language (a subset of Haskell) and covers most of the

<sup>&</sup>lt;sup>1</sup>http://en.wikipedia.org/wiki/Standard\_ML

<sup>&</sup>lt;sup>2</sup>http://www.cs.cmu.edu/~modelcheck/smv.html

<sup>&</sup>lt;sup>3</sup>http://web.cecs.pdx.edu/~mpj/goferarc/index.html

# 2 Related Work

features described in the Lipari guide. The author notes however that the implementation is aimed at prototype modeling and too slow for performance critical applications.

Anlauff introduces XASM, a component based ASM language compiled to C [4]. The novel feature of XASM is the introduction of a component model, allowing implementation of reusable components. XASM supports *functions* implemented in C using the *extern* keyword. CASM does not feature modularization, but can be extended using C code as well. XASM was used as the core of the gem-mex system, a graphical language for ASMs.

Gargantini et al. report on ASMETA [28]. Part of the development is a compiler translating ASM models into Eclipse Modeling Framework (EMF). The focus of this ASM implementation are high level models and design space exploration.

Farahbod designed CoreASM, an extensible ASM execution engine [23]. The CoreASM project is actively maintained and has a large user base. The CASM language is inspired by the CoreASM language, but over time they have diverged significantly.

Teich, Kutter and Weper describe a method to extract an ASM based instruction set description from a hardware description language [66]. This description is then used to automatically generate C code for a cycle accurate simulator of the processor. The Gem-Mex tool used provides support for implementing a parser which is used to read in assembler files for the simulator. Bit-true arithmetic functions are implemented in C and linked to the generated code. The feasibility of the approach is demonstrated by simulating very short programs on an ARM processor. No comparison to conventional simulators and no performance data are presented however.

# **Differentiation of CASM**

The available ASM tools are not implemented with efficient execution of ASM in mind. One reason is that ASM are often used to create high level models and explore the design space. Concrete implementations are written by hand and verified against the ASM model, often using model checkers. CASM differs from these approaches as it aims to be executed efficiently. Our models are not just specifications, but concrete and efficient implementations are synthesized. For that purpose we have developed an optimizing compiler. CASM is to the best of our knowledge the only ASM implementation offering symbolic execution.

# 2.3 First-Order Theorem Provers

Most state-of-the art theorem provers are based on the superposition calculus [6, 54]. Those provers try to perform proofs by *refutation*, i.e. by deriving an contradiction. A common classification of provers is whether they use an OTTER [50] style saturation algorithm or DIS-COUNT [5] style. The difference is in the treatment of generated clauses. As this set constantly grows the prover may need to remove *inferred* clauses at some point in time. DISCOUNT based prover therefore never utilize clauses from this set for inference or simplification. Schulz's E [62] prover is a modern, fast implementation based on DISCOUNT.

Vampire [59, 41] on the other hand implements both variants. Vampire is among the fastest theorem prover and has won the first-order section of the CASC [64] competition many years in a row now.

Satisfiability Modulo Theories (SMT) is another major branch in ATP. SMT is a generalization of the boolean SAT problem. Certain predicates in a SMT problem are interpreted using additional theories (hence the name SMT). The solvers for the theories (e.g. bit vector arithmetic) need to feed back results into the generic SAT solving part. A popular implementation is Microsoft's Z3 [21] prover. It is available under a shared-source license for many platforms.

Manna et al.'s STeP prover [49] has a rich graphical user interface allowing the user to guide the proof system. Counter examples can be derived automatically and debugging of problems is possible. STeP is an interactive tool, though, and its primarily intended for temporal specifications.

# **Differentiation of vanHelsing**

The proving tool developed in this thesis is solely *unification* based. In contrast to superposition based provers, it is not searching for a refutation of the problem but performing unification until a fix-point is reached. The conjecture must then be provable with the found unifications. This simplicity allows a very efficient implementation based on a graph data structure. The graph data structure can be visualized and allows graphical introspection and debugging of problems. We are not aware of a fully-mechanized prover which offers graphical proof introspection.

In contrast to SMT proving no background theories are implemented. Uninterpreted predicates are axiomatized using first-order formulae. This allows more flexibility, but may negatively influence performance.

restrain from equiring whether the name comes from the letters, the pillars, the leather, the place, or the mode of behavior Puck, The Sandman by Neil Gaiman

This chapter introduces the CASM language, its tools and focuses on the features distinguishing CASM from other ASM implementations. The novel technique of direct symbolic execution of ASM is formally defined and the implementation in the CASM interpreter is described. Further an efficient compilation scheme and an optimizing compiler are presented. During this thesis python prototypes of the CASM interpreter (including symbolic execution) and the compiler have been developed. The knowledge gained by the prototypes influenced the language design. A more efficient implementation of the interpreter using the C language was developed by Dominik Inführ in his bachelor thesis [36] under supervision by the author. The optimizing compiler was implemented by Philipp Paulweber in his master thesis [56] under supervision by the author. Interpreter and compiler are implemented as a single binary sharing the front-end (parser, type annotation, AST).

# 3.1 CASM - An Implementation of ASM

For a formal definition of CASM we refer to Gurevich's Lipari guide [31], Börger and Schmid's introduction of sequential execution [11] and Farahbod's CoreASM handbook [22]. More details on the CASM language can be found in [45]. An Extended Backus-Naur Form (EBNF) grammar can be found in appendix B. A novel feature of the interpreter is its capability to *symbolically execute* [39, 18] ASM models.

# 3.1.1 Types

The CASM language is statically typed and offers *Int*, *sub-range Int*, *Boolean*, and *String* as atomic types. Compound types are *List* and *Tuple*. There are no implicit type conversions

performed by CASM. If desired the programmer can convert types using the (range checking) built-in functions: *Int2Boolean, Boolean2Int, Int2Enum, Enum2Int.*

# 3.1.2 State

The central notion of ASM is the *state*. It is described using a set of *functions*. Each *function* has an arity. Let  $\overline{a}$  be an vector of arity n and f and n-ary function, then  $(\overline{a})$  is called a *location*. In ASM *functions* are mathematical objects and are therefore *defined* over their whole *range*. CASM functions are typed and programs are checked statically. A (finite) program only uses a *finite* subset of values (of the state). The special value *undef* is assigned to *locations* which have never been defined by the CASM program. *Undef* is a *continuation* of the underlying *function* which assures a mathematical sound model. This gives a sound semantics to programs reading undefined *locations*, in contrast to C's behavior which e.g. is undefined if a program reads undefined memory.

ASM *rules* (statements) do not change the *state* directly, but create *updates*. An *update* is a tuple  $(f(\overline{a}), v)$  which describes that the *location*  $f(\overline{a})$  was changed to value v. ASM rules are executed in parallel, the updates produced by rules are joined to an *update set*. An update set which contains more than one update to the same *location* is called *inconsistent*. Inconsistent update sets are a run-time error in CASM.

Each CASM program has a *top-level rule*. This distinct rule is executed repeatedly, until the program is terminated explicitly. Whenever the *top-level* rule *concludes* (function return) the update set is applied to the state in an *atomic* operation. Hence ASM programs have *transactional* semantics.

# 3.1.3 Rules

The following list briefly summarizes the most important rules implemented in CASM. Börger and Schmid [11] is an excellent reference and we use the notational conventions introduced there. All rules except the *call* rule have exactly the semantics given there (and we omit it here).  $R_i$  is a rule and  $t_j$ : *Type* is a term of the specific type. We omit the type specification for some terms if it is not needed to capture the semantics, but keep in mind that all terms are typed in CASM.

• Skip Rule: This rule does nothing and returns an empty update set.

$\mathbf{skip}$

• Update Rule: Creates an update for a *n*-ary function f, assigning v to  $f(\overline{a})$ .

$$f(a_0, a_1, \ldots, a_n) := v$$

• Block Rule: This is the most basic rule defining parallel composition of enclosed rules.

$$\{R_1R_2\ldots R_n\}$$

12

• Sequential Block Rule: All enclosed rules are composed using sequential execution semantics.

$$\{ \mid R_1 R_2 \dots R_n \mid \}$$

• **Conditional Rule**: The basic ASM conditional rule. The conditional expression must be of boolean type and the else-branch is optional.

if t: Boolean then  $R_1$  else  $R_2$

• Case Rule: An optional default case label is provided which will be executed if none of the given cases match the value of the conditional expression t. The types of all  $t_i$  must be equal to the type of t.

```

case t : Enum, Int, String of

t_0 : R_0

\vdots

t_n : R_n

default : R

```

endcase

• Forall Rule: The forall rule evaluates the rule of the body composing the resulting update sets in parallel. Rule *R* will be evaluated for each element of the set described by *t*, binding the element's value to *i*. *t* may be an *Enum* type in which case each element of the enumeration is used as value or a *List* (with obvious semantics).

forall i in t : Enum, List do R

• Iterate Rule: Turbo ASM's iterate rule iteratively evaluates R using the intermediate state of the previous iteration (sequential composition) until R's update set is empty.

```

iterate R

```

• Let Rule: This rule adds a variable v to the environment. v is assigned the value t and R is evaluated in this environment. CASM performs type inference so the type of v can be skipped in most cases.

let

$$v = t$$

in  $R$

• **Call Rule**: Basic ASM call semantics are defined as call-by-name which can be implemented by a so called thunk [8], but this mechanism is not very efficient. CASM therefore has a modified semantics of the *call* rule. All arguments are evaluated before being passed as arguments (one could simulate this with *let* rules in the basic ASM definition). This makes call-by-name equivalent to call-by-value which is what CASM actually implements. The other change is that a *call* rule is evaluated in a new (empty) environment.

This effectively reduces the scope of variables introduced by *let* and *forall* rules (and the scope of rule arguments). Dynamically scoped variables cannot be compiled efficiently and cannot be typed statically. For all arguments  $a_i$  of the rule R the type of  $a_i$  must match the type of the term  $t_i$ . ( $\mathfrak{A}$  is a state,  $\zeta$  the environment,  $\zeta \frac{x}{u}$  creates a new environment  $\zeta'$  which equals  $\zeta$  except that  $\zeta'(x) = u$ .  $\zeta \frac{x_0}{u_0} \frac{x_1}{u_0}$  is the obvious composition of the new environment operator and  $\zeta_{\emptyset}$  is the empty environment.)

$$\llbracket \textbf{call } R(t_0, \dots, t_n) \rrbracket^{\mathfrak{A}}_{\zeta} = \llbracket R \rrbracket^{\mathfrak{A}}_{\zeta_{\emptyset} \frac{a_0}{v_0} \dots \frac{a_n}{v_n}} \text{ where } v_i = \llbracket t_i \rrbracket^{\mathfrak{A}}_{\zeta}$$

• **Indirect Call Rule**: CASM supports indirect invocation of rules. This mechanism uses a slightly different syntax where *r* is an expression returning a reference to a rule. The semantics is otherwise identical to the *call* rule.

**call**

$$(r : RuleRef)(t_0, \ldots, t_n)$$

Further implemented rules are *print*, *debuginfo* (in accordance to [22]) and *assert*. The *debuginfo* facilities support named *channels* and CASM tools accept a list of active channels. Only the output produced by active channels is actually printed. The *assert* rule is in accordance to the *assert* statement of the C language.

# 3.1.4 Expressions

The common boolean operations *and*, *or*, *xor* and *not* are implemented for *Boolean* values. *Int* operations are +,-,\*,/ and modulo (%). Comparisons operators are <=,>=,!= and equality (=).

A standard library is provided by CASM providing the following operations: *cons, app* for list construction, *peek, tail* to extract the list head (and tail) and *hex* converts an *Int* to a *String* with its hexadecimal representation.

# 3.2 Direct symbolic execution of ASM

This section introduces symbolic execution of ASM and describes how it is implemented in the CASM interpreter. We first define the formal foundations of symbolic execution in the context of ASM. A way to represent symbolic trace as first-order logic predicates is given and the implementation is described.

### 3.2.1 Definition of a Symbolic ASM

In this section we introduce symbolic execution and present an extension of Gurevich's basic ASM definition [31]. We tried our best to extend the basic ASM in a most natural way and in the spirit of the original definition. Although we output *symbolic traces* as first-order logical predicates, the definition of a *symbolic ASM* is generic and output formats (e.g. for model checkers) could be generated as well. The remainder of this section discusses various design decisions and gives definitions S1-S5 of a *symbolic ASM*.

#### Symbolic Execution

Symbolic execution is a technique where input values for a program may be so called *symbols* representing any possible concrete value. When a symbolic value appears as argument to an operation the result of the operation becomes a *symbolic expression*. Assume an addition y = x+1 and let x be a *symbol*, y then becomes the *symbolic expression* x+1. Symbolic expressions itself may be used as arguments for operations, e.g. z = y\*2. The value of z would then become the *symbolic expression* (x + 1) \* 2. By construction *symbolic expressions* are expressions consisting of operations applied to *input symbols*. There may be multiple input symbols for a program and there must be a way to distinguish them.

Things get difficult (but interesting) when a symbolic expression appears as the conditional in a control flow statement. The exact program continuation can't be determined and execution is forked to consider all paths. Instead of a single trace a tree of possible traces is generated. The continuation chosen on a fork point implies a condition for the (symbolic) conditional (i.e. conditional evaluated to true or false). The sum of all those conditions is called the *path condition*.

A system performing symbolic execution can without loss of generality create a *fresh* (never used before) symbol for each *symbolic expression* and only operate on symbols. We assume such a system for the remainder of this paper and use *symbolic expressions*, *symbol* and *symbolic value* synonymous.

#### The Symbolic Universe

All *basic* ASM [31] contain the special null-ary function *undef* to deal with partial functions. One could allow symbols to represent that value, but we think it is in the spirit of the basic ASM definition that symbols cannot represent the value *undef*. We define symbols to be a distinct sort (although compatible to other sorts), therefore:

All symbolic values are elements of this universe. Following the rule that *undef* is not part of any universe we state:

$$s \in Symbol \implies s \neq undef.$$

(S2)

A symbolic value is an unknown but concrete value, whereas *undef* is used to express the value of an undefined location. In that sense the definition is natural. Finally it is important to note that symbols can be uniquely identified (e.g. by numbering them), or in other words

The equality operator (=) is defined for all

$$s_1, s_2 \in Symbol.$$

(S3)

Summarizing S1-S3 a *symbolic ASM* contains at least 2 universes (*Boolean* and *Symbol*). All symbols are unique and part of the *Symbol* universe, they cannot represent the value *undef*.

#### **Symbolic Functions**

To perform symbolic execution a way to provide input symbols to the ASM programs is needed. Similar to *undef* being a continuation of partially defined functions, we define a symbolic continuation of partially defined symbolic functions. Partially defined *symbolic* functions are continued using pairwise distinct *symbols*. Obviously this definition implies an infinite number

of symbols for infinite domains. This allows to model systems with an unknown or unbound number of *input symbols*. In section 3.2.3 we present a technique to efficiently handle infinite domains.

In ASM different types of functions (e.g. *static* for read-only) are possible. We add a new function type – *symbolic* – which can be combined with the existing types. Only *symbolic* functions are continued with pairwise distinct symbols.

Functions tagged symbolic  $\implies$  associated locations to be symbolic. (S4)

Each *symbolic* location contains a unique symbolic value. (S5)

## 3.2.2 Mapping Symbolic Traces to First Order Logic

While building *symbolic expressions* is well understood, presenting them for further processing is an open issue. There is no single, clearly superior solution to the problem. Various authors proposed different solutions, all suited for their special needs. Boyer's [12] SELECT tool allows the user to symbolically execute a program under his interactive control to support manual proving of properties. Khurshid et al. [38] generate output for model checkers supporting non-deterministic choice. Coen et al. [19] present symbolic expressions in the path description language (PDL) output and process them using the SAVE tool.

We wanted a human readable format also suitable for automated processing and proving tools. First-order theorem-proving is a mature branch of automated theorem proving with a number of commercial and free provers available (e.g. Isabelle [55], SPASS [67] or Otter [51]) and is well suited for our needs. The TPTP language proposed by Sutcliffe et al. [65] is a text based format understood by a wide range of automated theorem provers. We therefore decided to generate *symbolic traces* as first-order logic formulas in TPTP format. Each trace created describes exactly one path the program takes while being executed symbolically.

There is a semantic gap between a bunch of logic formulas and a trace describing a (symbolical) program execution. The later has a notion of time whilst a set of logical formulas is not time-aware. The remainder of this section describes how to map *symbolic expressions* and the changed *state* produced by each computation step to first-order formulas.

#### Mapping of State and a Notion of Time

The basic idea is to map the value v of a location  $f(\overline{a})$  to a predicate  $f(\overline{a}, v)$ . Locations can change their value over time, therefore they cannot be mapped to a logical predicate directly. One needs to add a notion of time. We add a logical time-stamp as an additional (first) argument to functions.

For a basic ASM, only consisting of synchronous parallel updates, a notion of time is easy to give. Gurevich argues that each step of the computation corresponds to a tick of the logical clock [32]. Assume the ASM (infinitely) executing  $\mathbf{rule} = x := x + 1$ . The trace of predicates resulting of this program would be the (infinite) set  $\{x(t, x_i + t) : t = 0, 1, ...\}$  where  $x_i$  is the initial value of the function x.

A critical question is how to measure (logical) time in presence of the *sequential block* rule. Consider a parallel block containing a sequential block, i.e.

$$\{ \\ \{ | R_1 R_2 | \} \\ R_3 \\ \}$$

Clearly the time-stamp for rule  $R_1 < R_2$ , as  $R_1$  is executed before  $R_2$ . On the other hand both of them are executed in parallel to  $R_3$ . So  $R_3 = R_1 \wedge R_3 = R_2$  also is an arguable requirement for the time-stamps. Obviously these requirements are contradicting. Following the definition of hidden internal computation steps (Fruja and Stärk [26]) we simply do not emit predicates for sequential block internal state changes at all. As a consequence, the model must make all state transitions an application wants to reason about non-hidden. We think this is reasonable.

After each computation step of the (symbolic) ASM, predicates for all symbolic locations are written to the *symbolic trace*. The logical time-stamp of each of the predicates equals the number of computation steps the ASM performed so far. Due to definition S5 there is an infinite number of symbolic locations if there is at least one symbolic function with an infinite domain. Obviously only a *relevant* subset of symbolic locations can be written to the symbolic trace. For now we vaguely define the *relevant set* as the set of symbolic locations the application using the symbolic trace is interested in. In section 3.2.3 we present a solution to this problem.

The initial state is assigned logical time 1. The final state is (additionally) labeled with logical time 0. Thus the time-stamps of the initial and final states are always known which is comfortable for many proofs.

#### Mapping of Symbolic Expressions - DFT

At the beginning of program execution only *input symbols* exists. During program execution more complex *symbolic expressions* are built (by applying operators to symbols). Internally we use fresh symbols to abbreviate complex symbolic expressions. A simple inductive argument shows that each fresh symbol implicitly represents a tree of of *input symbols* and operators.

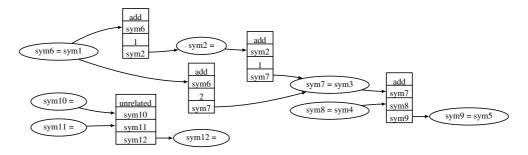

We therefore map each application of a *n*-ary ASM operator to a *n*+1-ary predicate. The additional (last) argument is a fresh symbol (the result of the operation), the name of the predicate is the name of the operator. Again assume the program calculating y := x + 1 and z = 2 \* y yielding the symbolic expression 2 \* (x + 1) for z and let x be the (input) symbol sym1. The addition will be mapped to the predicate add(sym1, 1, sym2) where sym2 is a fresh symbol. This can be read as: it is true that the result of the addition of sym1 and 1 is named sym2. Next the multiplication will be mapped to mul(2, sym2, sym3) with a fresh symbol sym3.

One may wonder about expressions modifying intermediate state inside of a *sequential block* rule. Although the intermediate state is not visible in the *symbolic trace* it may be updated and read by expressions. The above argument however showed that *symbolic expressions* are expressed solely by means of *input symbols* and operator application. An update may store a

symbolic expression to an intermediate location, if it should be read again it is the symbolic expression itself, not the state, that matters.

Actually the state is completely transparent for expression evaluation. Consider for example the following ASM program fragment: {| x := x + 1; x := x \* 2 |}, further assume x to contain the symbolic value sym0. The addition operator creates a fresh symbol sym1 representing sym0 + 1 and updates x. The multiplication operator creates a fresh symbol sym2 representing sym1 \* 2. This will be mapped to the two predicates add(sym0, 1, sym1) and mul(sym1, 2, sym2), correctly representing the resulting symbolic expression but without any reference to the (intermediate) state x.

In our proof applications the input symbols are mapped to program variables and registers. The *symbolic expressions* directly correspond to the concept of Data Flow Tree (DFT) which is implicitly described by the predicates.

## 3.2.3 Implementation of Symbolic Execution in CASM

This section describes the implementation of symbolic execution in the CASM interpreter.

#### Lazy Initialization of Symbolic Functions

As indicated in section 3.2.2 one needs to identify a *relevant subset* of symbolic locations to be written to the *symbolic trace* after each computation step of the ASM. The CASM implementation uses a technique called *lazy initialization* (Khurshid et al. [38]). A fresh symbol is created for a *symbolic location* when it is accessed for the very first time. Therefore a CASM symbolic trace contains the (finite) set of all symbols ever accessed during program execution. Unless the application wants to reason about locations *not* affected by the CASM program it is justified to assume that this set forms a super-set of the *relevant* set.

Two problems need to be considered implementing lazy initialization of symbolic functions. A symbolic location  $f(\overline{a})$  may first be accessed in computation step n > 1, leading to creation of a fresh symbolic value  $s_k$ . All symbols accessed in a symbolic function are considered to be *input symbols*. Therefore predicates for all previous computation steps have to be emitted as well. This allows to reason about symbolic value in the preceding steps (including the initial one).

The second problem is due to the tree structure of currently active intermediate states induced by *sequential block* rules. Assume two rules  $R_x$  and  $R_y$  both accessing the same uninitialized symbolic location  $f(\overline{a})$  and the following context:

```

\{ \\ \{ | R_1 R_x | \} \\ \{ | R_2 R_y | \} \\ \}

```

The intermediate states used to evaluate  $R_x$  and  $R_y$  are different, nonetheless the implementation of symbolic execution has to assure that both rules read the same symbolic value for  $f(\overline{a})$ .

#### **Trace Output Format**

TPTP is a human-readable text based format in essence consisting of *annotated formulas* with the following general form: language(name, role, formula). The language specifies the type of the formula, we exclusively use first-order forms with the language specifier fof. While *name* is an otherwise ignored arbitrary identifier, *role* specifies the user semantics of the formula (e.g. axiom, hypothesis, conjecture). An example of a formula is fof(id, hypothesis, sym3 = 5) stating that the constant term *sym3* equals to 5.

# An Example

Consider the CASM program (fragment) given in listing 3.1 which swaps and increases values of *foo* and *bar* with *bar* being symbolic. Listing 3.2 shows the symbolic trace resulting from a single evaluation of rule r.

```

1

function (symbolic) foo : -> Int

2

initially {3}

3

function (symbolic) bar : -> Int

4

5

rule r = \{

6

{ |

7

foo := bar

fof(0, hypothesis, bar(1, sym2)).

fof(1, hypothesis, add(sym2, 1, sym3)).

fof(2, hypothesis, foo(2, sym3)).

8

foo := foo + 1

9

|}

10

bar := foo + 1

fof(3, hypothesis, bar(2, 4)).

11

}

```

Listing 3.1: Swap and increment

Listing 3.2: Symbolic trace in TPTP

Line 7 in the program corresponds to line 1 in the trace. The location *bar* is used by the update rule (assignment) which triggers creation of the symbol *sym2*. This symbol is temporarily stored at location *foo*, but this is a hidden intermediate state not visible in the trace. Line 8 (of the program) triggers the output of the *add* predicate describing the addition which creates a *symbolic expression* named *sym3* (line 2 in of the trace). Finally *sym3* is assigned to location *foo*, which can be seen in line 3 of the trace. In line 4 of the trace one sees that location *bar* contains the concrete value 4 (*foo* was initially 3 and the sequential block is executed in parallel to this update, so foo is still 3 here) after the first computation step (logical time is now 2).

#### **Semantic Annotation**

For some proofs it is useful to know when exactly a certain *symbolic location* was accessed for the very first time. Assume this happens at logical time t. As the symbolic value existed since the initial state (and will exist till the final state unless updated), the trace contains predicates for all this logical times. The trace alone is therefore not sufficient to determine time t. The predicates emitted for times less than t are therefore annotated by appending the TPTP comment \$SYMBOLIC at the end of the line. Predicates emitted when a symbolic location is accessed the very first time are annotated with the comment \$CREATE. Although the annotations for

1

2

3

4

5

predicates corresponding to the update of a location (%UPDATE) are redundant and could be extracted from the trace, they are added to ease the programming of validators.

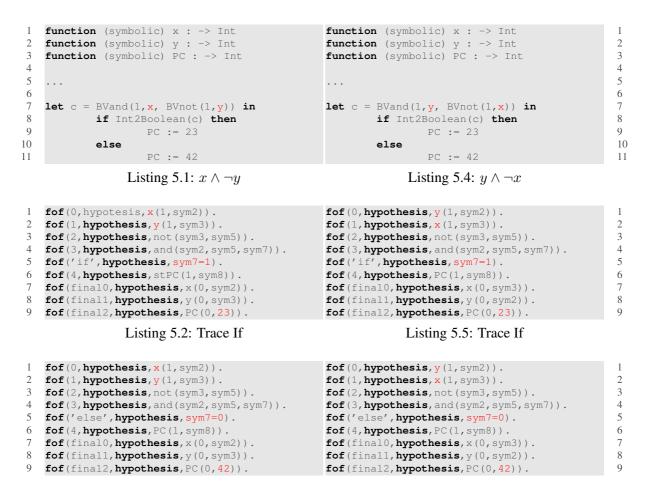

#### Symbolic Control Flow

In the CASM language we implemented symbolic execution for *if-then-else* and *case* rules. When the conditional expression of the rule is a symbolic value, all continuations are possible. That is *if-branch* taken or (optional) *else-branch* taken for *if-then-else* and each of the *cases* (including an optional *default* case) taken for the *cases* rule. Program execution needs to be forked and continued for each of the possible continuations. Each continuation writes its trace to a separate trace file, so the application can reason about different paths taken by the program. Which continuation has been chosen induces a constraint for the symbol presenting the conditional expression. Those constraints are memorized in a *path condition* store and further control flow decisions on the symbolic values are evaluating the store. This eliminates the creation of contradicting traces.

The path condition is crucial for proving program properties. Listing 3.3 illustrates the importance. The code assures that no division by zero can occur, but this can only be proven utilizing the path condition in listing 3.5.

|   | Listing 3.3: Path Condition                  | <pre>fof(id0, hypothesis, x(0, sym2)). fof('else', hypothesis, sym2!=0).</pre> | 1<br>2 |

|---|----------------------------------------------|--------------------------------------------------------------------------------|--------|

| 1 | if x = 0 then skip                           |                                                                                | 3      |

| 2 | <b>else</b> foo := 12 / x                    | <pre>fof(id1, hypothesis,</pre>                                                | 4      |

|   |                                              | divide(12, sym2, sym3)).                                                       | 5      |

| 1 | <pre>fof(id0, hypothesis, x(0, sym2)).</pre> | <pre>fof(id2, hypothesis, foo(0, sym4)).</pre>                                 | 6      |

| 2 | <pre>fof('if', hypothesis, sym2=0).</pre>    | <pre>fof(id3, hypothesis, foo(1, sym3)).</pre>                                 | 7      |

|   | Listing 3.4: <i>if-branch</i>                | Listing 3.5: else-branch                                                       |        |

Line 2 in both listings (3.4 and 3.5) shows the emitted constraint. A theorem prover could now be used to prove that listing 3.3 is division-by-zero free (by proving both traces to be division-by-zero free).

# **3.3 Efficient Compilation of CASM**

The CASM language is designed with efficient compilation in mind (static type system, callby-value for rule invocations). As part of this work a prototype implementation of a CASM compiler has been developed in python. Knowledge gained from this implementation has been used to refine the language design. Performance critical issues of the run-time system have been identified and an optimizing compiler has been designed. Theses ideas have been implemented by Philipp Paulweber in his master thesis [56]. Details on the analysis framework and run-time implementation are published in an article by Lezuo, Paulweber and Krall [48].

We will give a brief explanation of the main ideas behind the CASM compiler here. The run-time is based on the assumption that the *state* of the compiled programs is larger than the *update sets*.

## 3.3.1 Dynamic Memory Allocation

Only *functions* and updates need to be allocated dynamically. Due to the transactional semantics of ASM languages the life-span of an update is exactly one *step* of the machine. A pre-allocated memory pool is used to store updates until a *step* is made and all updates are committed to the function storage. This pool can simply be reused in subsequent steps (dump-allocation). The run-time therefore has virtually no memory management overheads.

## 3.3.2 Storage for CASM Functions

To properly implement *functions*, set operations are necessary. All *locations* which are not explicitly defined otherwise have the special value *undef* (demanding an *is-element-of* set operation). A distinct hash-map (with linear probing) is used as storage for each *function*. The function arguments are concatenated to form the key. Each slot of the map has two special properties, *undef* and *branded*. The *undef* property is set if the *location* has the special value *undef*. An update may set a previously defined *location* to *undef*, so such *locations* need to be tracked explicitly. A slot is *branded* when its corresponding *location* is accessed for the first time. (*Branding* allows to use other default values than *undef*, CASM supports this feature). The run-time uses the slot's address, which must be guaranteed to be stable, as a unique identifier.

After each *step* of the machine the hash-map can safely be enlarged, if the load factor should have become too large. In the rare case that during a single *step* the hash-map would overflow, additional memory is allocated. In-between the next machine *step* the hash-map is resized and the overflow memory gets merged.

If a sub range integer type is used for the domain of a CASM function, an array is used as *function* storage instead of a hash-map (for reasonable sizes of the domain). An additional byte is needed to keep track of the special value *undef*.

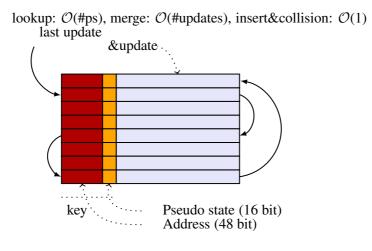

#### 3.3.3 Updates and Pseudo States

Due to the interleaving of parallel and sequential execution semantics the state used to evaluate a statement and the state affected by its updates are in general not equal [26]. Listing 3.6 illustrates the problem.  $stmt_1$  and the sequential blocks containing  $stmt_2$  and  $stmt_4$  are in a parallel block. Therefore they are evaluated under the same state  $S_0$ , their updates however are applied to different states. While updates produced by  $stmt_1$  are applied to  $S_0$ , updates produced by  $stmt_2$  are used to create a *temporary* state  $S_1$ . The sequential composition with  $stmt_3$  may modify updates produced by  $stmt_2$  and only the resulting update set will be applied to  $S_0$ . The same situation is with  $stmt_4$  and  $stmt_5$ . As e.g.  $stmt_4$  may contain a nested parallel block a tree-like structure of states is created. The nesting of update sets is very similar to nested transactions in software transactional memory (STM) [2]. The major difference is that an STM transaction aborts when reading an object for which a commit is pending while in ASM read access can never fail. Multiple updates to the same *location* in a parallel context is a run-time error (*inconsistent update*) in CASM.

Our assumption is that the number of updated *locations* (in a single ASM step) is much smaller than the whole state of the program. We therefore do not duplicate the state but keep

## 3 CASM - Efficient Abstract State Machines

$stmt_1$ { |  $stmt_2$  $stmt_3$ | } { |  $stmt_4$  $stmt_5$ | }

## Listing 3.6: Interleaving PAR/SEQ

track of all updates produced so far in a data structure called *update set*. When looking up a *location* the run-time has to query the *update set* for updates affecting the current state (due to sequential execution semantics).

We use the notation of *pseudo state* to keep track of updates affecting the current state. The *pseudo state* is a counter which is increased (at run-time) when a block with *different* execution semantics is entered. When a block is left (and control-flow returns into a block with *different* execution semantics) the *update set* is merged into the *update set* of the surrounding block. This is a serialization of the (partial) parallel execution semantics of ASM. Initially the system starts in parallel execution state, so *pseudo state* 0 denotes a block with parallel execution semantics. When entering a block with sequential semantics the *pseudo state* will be increased by 1. By construction this counter is odd when executing a block with sequential execution semantics and even when in parallel mode.

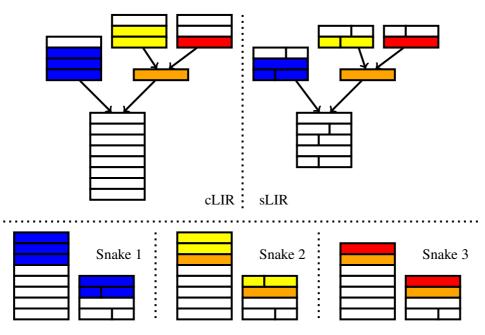

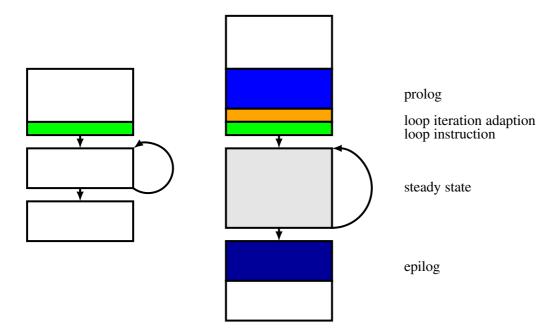

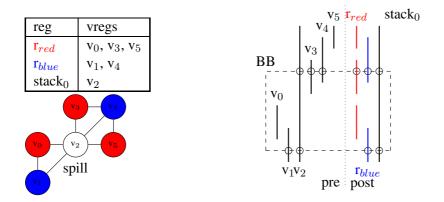

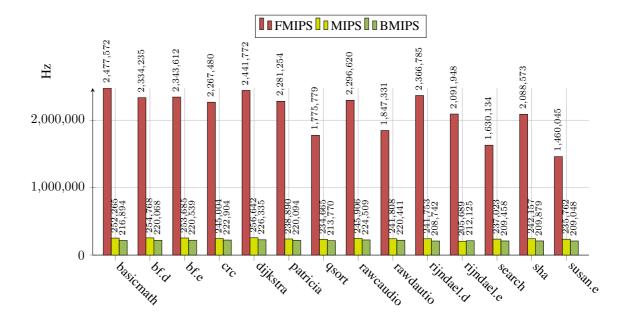

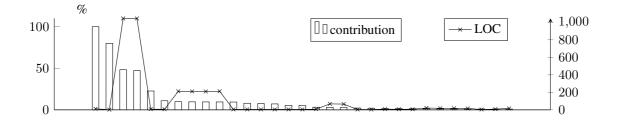

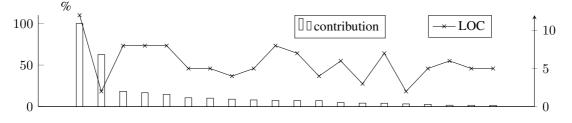

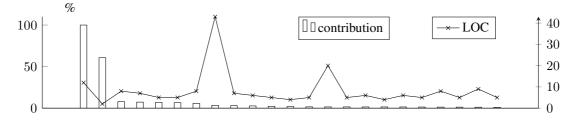

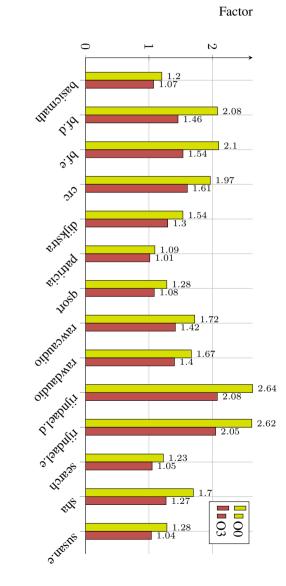

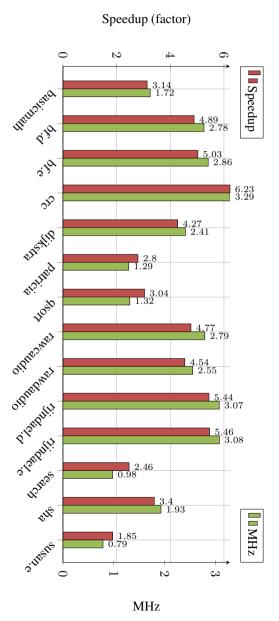

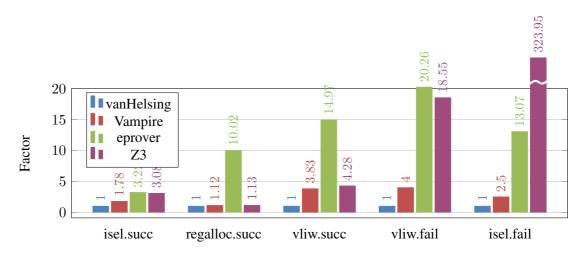

The *update set* is implemented as a hash-map. The keys are 64 bit values, the lower 16 bits are the *pseudo state* of the block the update originates from, the remaining bits are the lower bits of the slot used to store the *location*. (This limits the number of nested states to 65536 and the keys may collide for slots whose addresses only differ in the uppermost 16 bits. A key collision triggers an erroneous program abort, but no wrong behavior. We never hit any of the limits in our applications.)